BIT外围硬件设计

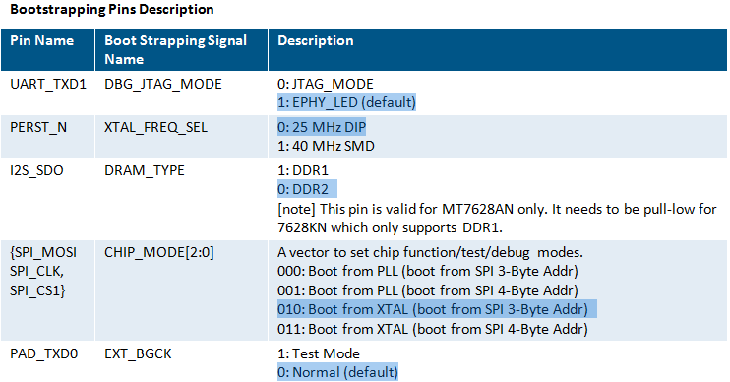

MT7688启动模式相关引脚

具体7688启动模式如下图:

| 描述 | 模组已做处理 |

|---|---|

| I2S_SDO | 4.7K下拉 |

| SPI_CS1 | 3B模式:4.7K下拉,4B模式:4.7K上拉 |

| SPI_CLK | 4.7K上拉 |

| SPI_MOSI | 4.7K下拉 |

| UART_TXD0 | 4.7K下拉 |

| UART_TXD1 | 4.7K上拉 |

4B模式的BIT3由于核心板没有针对SPI_CS1上拉,所有需要底板设计时给SPI_CS1预留一个1K的上拉电阻。

串口控制台(适用BIT3、BIT4)

控制台UART_RX0设计时,外部请考虑上拉电阻到3.3V,例如10K、4.7K、3.3K等等。防止UART_RX0受到干扰情况下执行“命令”。

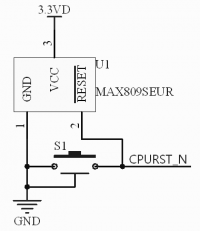

免焊救砖(适用于歪朵拉出品的所有7688硬件)

免焊救砖指的是如果UBOOT损坏了,我们就称板子变砖了,虽然几率极小,但也只能使用SPI编程器对板子进行“救砖操作”

而免焊救砖指的是在不需要把FLASH芯片焊接下来的情况下,利用SPI编程器的SPI接口连接BIT模块的SPI0对应管脚进行救砖。

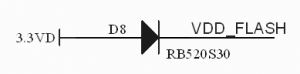

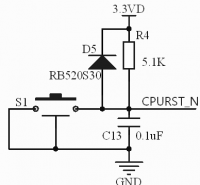

BIT模块相较市面上其他模块,这部分特性把FLASH的供电独立了出来。推荐用户为了量产后维护方便,可以将SPI_MISO、SPI_MOSI、SPI_CLK、SPI_CS0、VDD_FLASH预留焊盘。

VDD_FLASH供电(适用BIT3)

BIT4,BIT5的VDD_FLASH引脚无需用户处理